1 基本概念

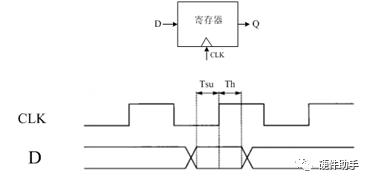

建立时间Tsu:器件输入端在时钟信号有效沿到来前,要求输入信号稳定不变的时间。

保持时间Th:器件输入端要求输入信号在时钟信号有效沿到来后保持稳定不变的时间。

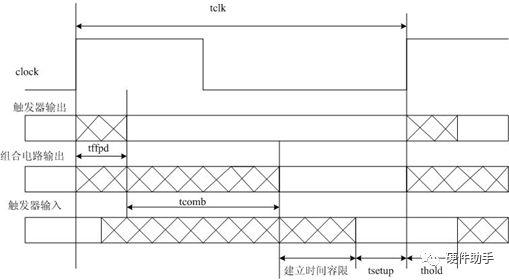

输出延时Tco:器件的输出延迟时间由两部分组成。一是触发器输出响应时间(Tffpd)。可以理解为触发器在CLK有效沿到来后输入到输出的延时时间,也可以理解为输出延迟。另一个是触发器输出的变化经过组合逻辑元件所需的附加时间,一般是组合逻辑延迟(Tcomb)。

电路的线延迟Tdelay:是指上级电路的输出到下级电路的输入之间的电路延迟。

时钟延时Tpd:时钟延时。

2 时序要求

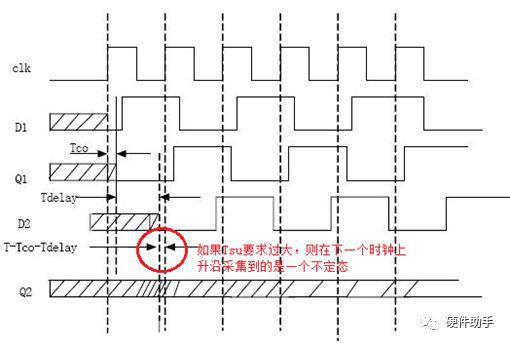

2.1 时钟没有延时的情况

建立时间容限是指器件允许的安全的建立时间长度范围。同样保持时间容限就是器件允许的安全的保持时间长度范围。一般来说建立时间容限和保持时间容限都大于等于0。

Tclk=Tco+Tdelay+建立时间容限+Tsu

所以建立时间容限=Tclk-TcoMAX-TdelayMAX-Tsu>=0

Tsu<=Tclk-TcoMAX-TdelayMAX

即时钟周期T必须能容纳触发器寄存器的最大传播延时(输出延时)、电路的最大延时以及建立时间的要求,即Tclk>=TcoMAX+TdelayMAX+Tsu。

如果第二个触发器的Tsu不满足要求,第二个触发器在第二个时钟的上升沿将采到的是一个不定态,那么电路将不能正常的工作。

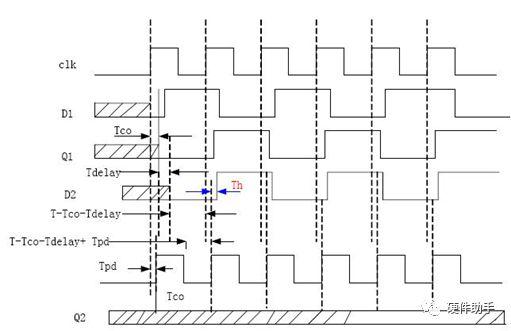

对于数据接收端来说,任何时钟沿采样的数据,都是发送端前一时钟周期发送的数据。发送端可能每个时钟周期都要发送数据,那么对于接收端来说,任何一个时钟沿后一段时间,数据线上的数据都会被发送端第二次发送的数据改变,所以保持时间容限其实是由于下一个时钟节拍上的数据引起的。

信号在时钟信号有效沿跳变,但真正到达下一级输入端的的跳变发生在时钟信号有效沿后的Tco+Tdelay时刻。为了保证时序元件的输入数据在时钟边沿之后能维持足够长的时间,而不会引入新数据而造成输入不稳,所以要求寄存器最小传播延迟和电路最小延时要大于寄存器的保持时间,即:Th<=TcoMIN+TdelayMIN。保持时间容限=TcoMIN+TdelayMIN-Th。

从上面的时序分析可以看出,第二级触发器的建立时间与保持时间与第一级触发器的建立与保持时间是没有关系的,而只和第二级触发器前面的线路延时和第一级触发器的数据传输延时有关,说明延时没有叠加效应。

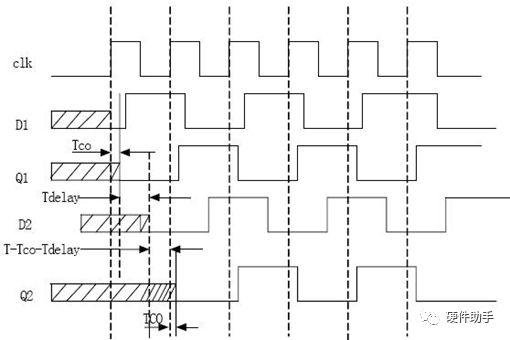

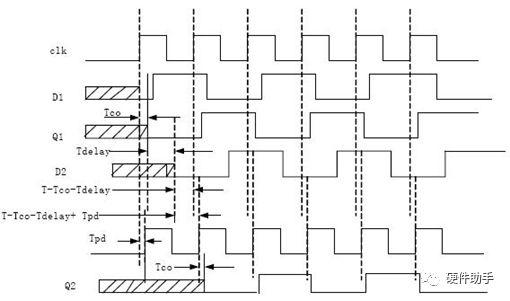

2.2 有时钟延时的情况

如果时钟存在延时,这种情况下就要考虑保持时间了,同时也需要考虑建立时间。时钟出现较大的延时多是采用了异步时钟的设计方法,这种方法较难保证数据的同步性,所以实际的设计中很少采用。

对建立时间放宽了Tpd,所以D2的建立时间需满足要求:

Tsu<=Tpd+Tclk-TcoMAX-TdelayMAX

由于建立时间与保持时间的和是稳定的一个时钟周期,如果时钟有延时,同时数据的延时也较小,那么建立时间必然是增大的,保持时间就会随之减小,如果减小到不满足D2的保持时间要求时就不能采集到正确的数据。

即Tclk-(Tpd-Tco-TdelayMIN)<Th就不满足要求了,所以D2的保持时间应该为:

Th<=Tclk-(Tpd-Tco-TdelayMIN)

上式可以看出,如果Tpd=0,也就是时钟的延时为0,那么同样是要求Tco+TdelayMIN>Th,但是在实际的应用中由于线路的延时远远大于触发器的保持时间,所以不必要关系保持时间。

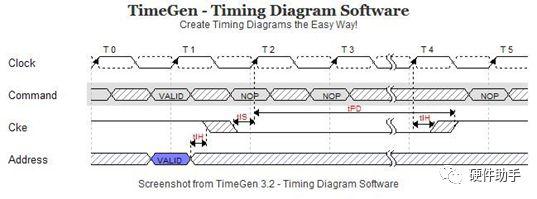

3 时序生成工具

3.1 TimeGen

TimeGen是一个用户画时序图的CAD工具,其时序图波形可以复制并粘贴到其他应用程序,用于书写设计规范。可以把时序图转成ASCII,然后复制到Verilog/VHDL的文件中。

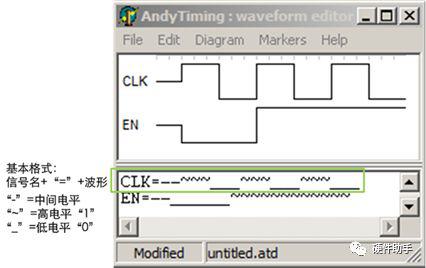

3.2 AndyTiming

AndyTiming是用符号代码代表单位时间内的波形。

网上的一些使用评价如下:

绘制的波形非常清晰(甩仿真波形截图好几条街)并且可以导出变成bmp文件,非常适合放到文档或者ppt里面。波形代码还可以保存成.atd文件以方便下次调用。

添加文字方面比TimeGen好太多。

等于号必须要对齐,手动对齐有点不方便。

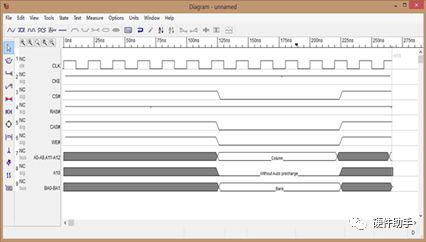

3.3 TimingDesigner

TimingDesigner既用于系统级设计,用于时序分析和文档编制,也用于ASIC/FPGA设计中,用于接口规范,以及创建SDC时序约束。TimingDesigner更专业,也要更复杂一些。

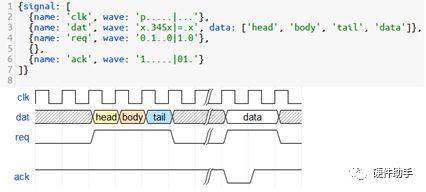

3.4 WaveDrom

WaveDrom是一个基于js的画时序图的工具。较AndyTiming功能更强大,画得也更漂亮,不过上手就复杂一些了。可以在线画,也可以下载本地版。