LPDDR4зү№жҖ§

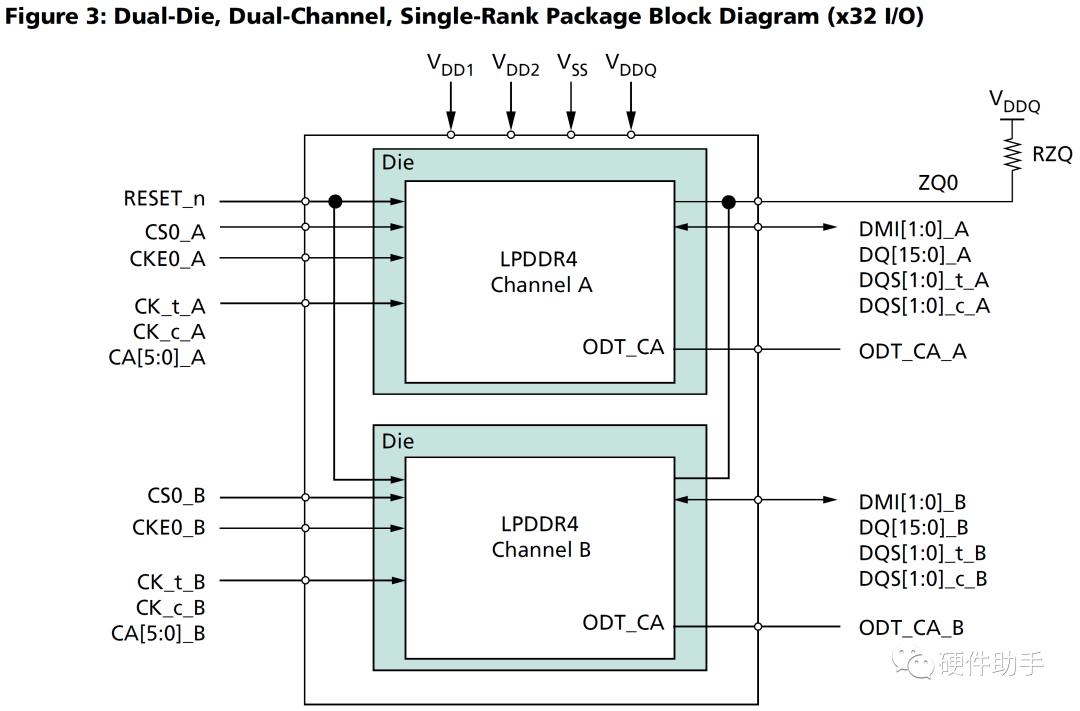

LPDDR4жңҖж—©жҳҜз”ЁдәҺ移еҠЁжүӢжңәзҡ„DRAMпјҢдҪҶйҡҸзқҖ科жҠҖзҡ„еҸ‘еұ•пјҢе·Із»Ҹжҷ®еҸҠеҲ°дәҶе№іжқҝз”өи„‘гҖҒ笔记жң¬гҖҒеөҢе…ҘејҸи®ҫеӨҮдёӯгҖӮLPDDR4иғҪеңЁеҫҲе°Ҹзҡ„PCBйқўз§Ҝе’ҢдҪ“з§ҜдёҠжҸҗдҫӣдәҶе·ЁеӨ§зҡ„еёҰе®ҪпјӣеңЁ4266Mbpsзҡ„ж•°жҚ®зҺҮдёӢпјҢеҪ“дёӨзүҮDieе°ҒиЈ…еңЁдёҖиө·ж—¶пјҢеҚ•дёӘ15жҜ«зұіx15жҜ«зұіLPDDR4е°ҒиЈ…еҢ…еҸҜжҸҗдҫӣ34 GByte/sзҡ„еёҰе®ҪгҖӮLPDDR4е»әз«ӢеңЁLPDDR2е’ҢLPDDR3зҡ„жҲҗеҠҹеҹәзЎҖд№ӢдёҠпјҢеўһеҠ дәҶж–°зҡ„зү№жҖ§е№¶еј•е…ҘдәҶдё»иҰҒзҡ„з»“жһ„еҸҳеҢ–гҖӮ

LPDDR4иҝһжҺҘж–№ејҸ

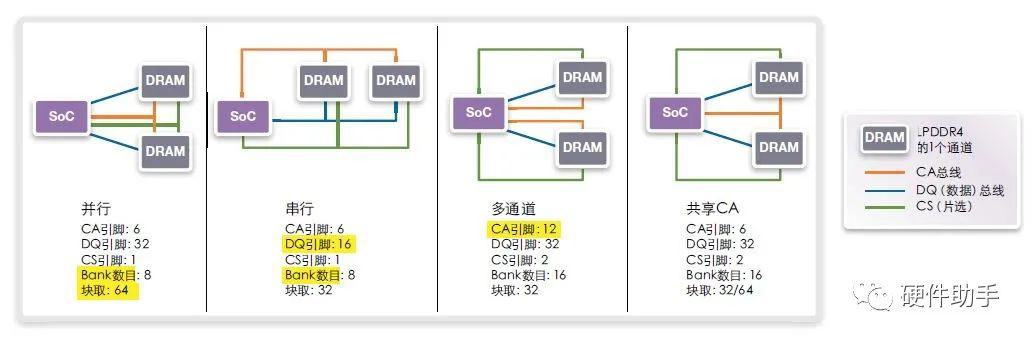

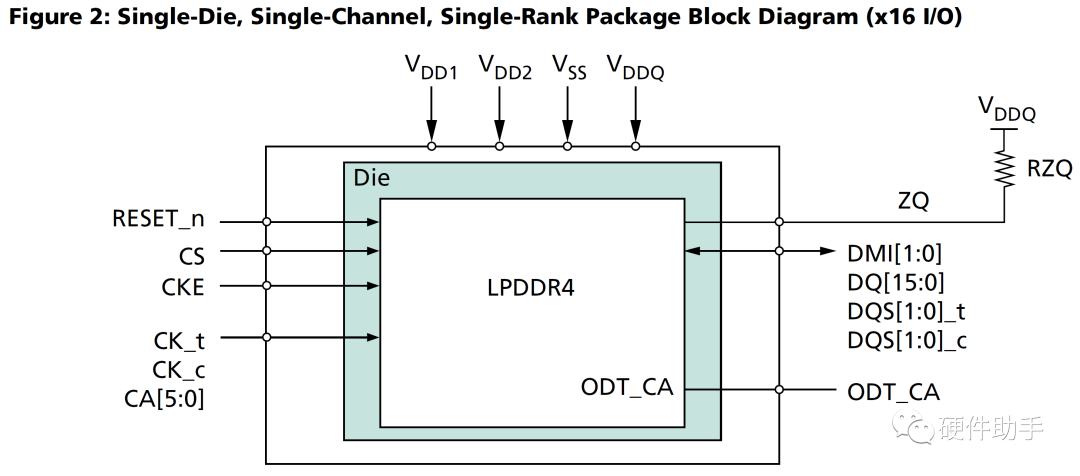

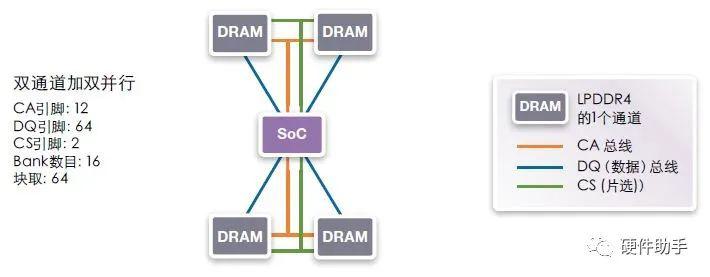

еҜ№дәҺеҸӘжңүдёҖдёӘchannelзҡ„еҚ•зүҮDDRеҷЁд»¶пјҲжҜ”еҰӮLPDDR3зҡ„еҚ•dieе°ҒиЈ…пјүпјҢзӣҙжҺҘйҮҮз”ЁP2PиҝһжҺҘеҚіеҸҜпјҢеҜ№дәҺжңүдёӨдёӘchannelзҡ„еҚ•зүҮDDRеҷЁд»¶пјҲжҜ”еҰӮLPDDR4зҡ„еҚ•Rankе°ҒиЈ…пјүпјҢеҸҜд»Ҙж”ҜжҢҒеӨҡз§ҚиҝһжҺҘж–№ејҸгҖӮ

LPDDR4дҝЎеҸ·

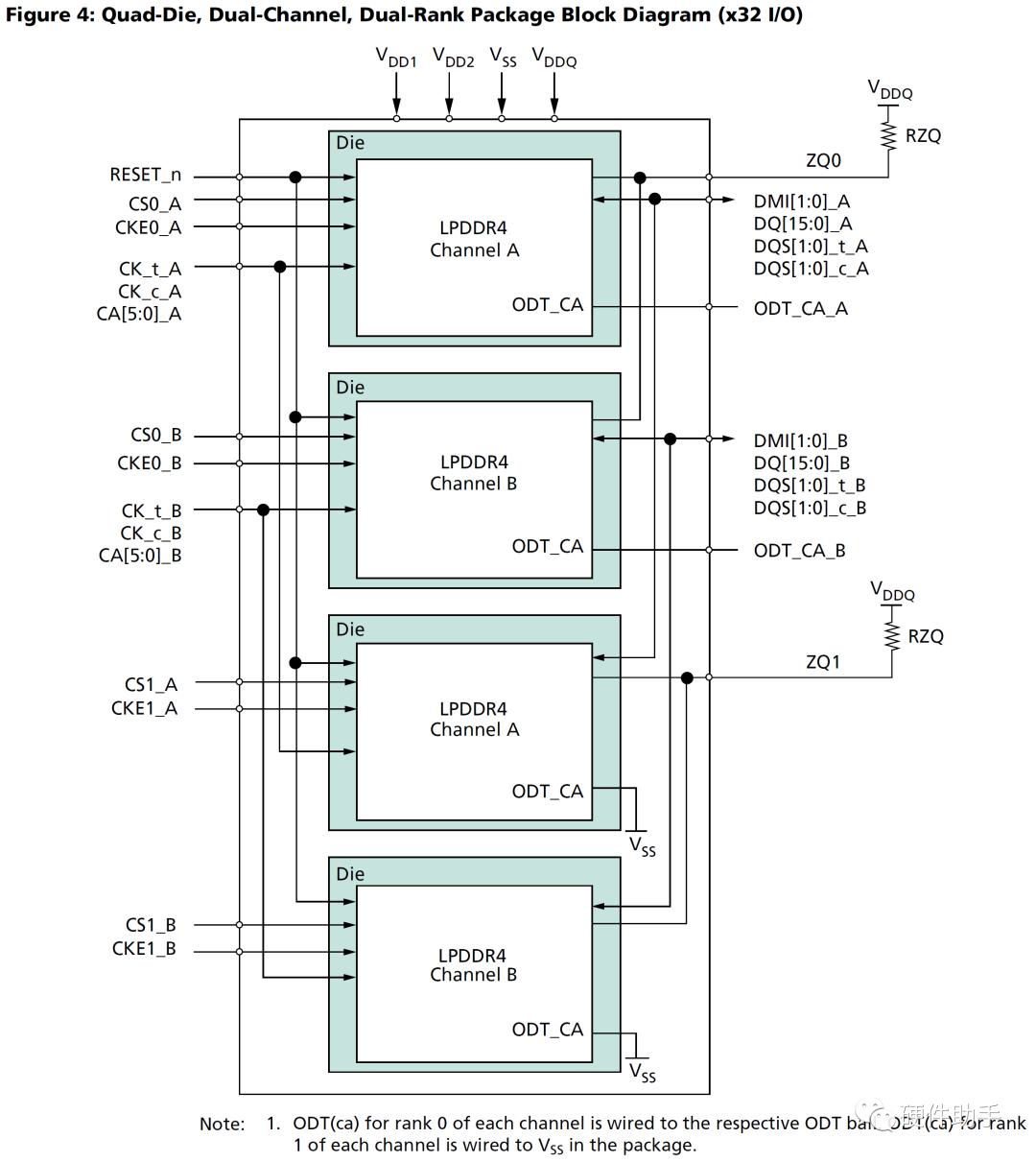

LPDDR4зҡ„дҝЎеҸ·еҢ…жӢ¬еҮ еӨ§зұ»пјҡ

е·®еҲҶж—¶й’ҹпјҡжҜҸдёӘйҖҡйҒ“йғҪжңүиҮӘе·ұзҡ„ж—¶й’ҹпјҢең°еқҖе‘Ҫд»ӨжҺ§еҲ¶дҝЎеҸ·еңЁCK_tзҡ„дёҠеҚҮжІҝCK_cзҡ„дёӢйҷҚжІҝйҮҮж ·пјӣ

ж—¶й’ҹдҪҝиғҪдҝЎеҸ·пјҡй«ҳз”өе№іжңүж•Ҳпјӣ

зүҮйҖүдҝЎеҸ·пјҡжҜҸдёӘdieйғҪжңүиҮӘе·ұзҡ„зүҮйҖүдҝЎеҸ·пјӣ

е‘Ҫд»Өең°еқҖдҝЎеҸ·пјҡеҢ…еҗ«е‘Ҫд»ӨпјҢең°еқҖдҝЎжҒҜгҖӮLPDDR4 йҮҮз”Ёзҡ„жҳҜCBTпјҲcommand bus trainingпјүзҡ„CA training зҡ„иҝҮзЁӢпјҢеңЁиҝҷз§Қж–№ејҸдёӯпјҢдјҡиҝӣиЎҢVrefCaпјҢCLK еҜ№CSпјҢCLK еҜ№CA зҡ„ж—¶еәҸи°ғж•ҙпјӣ

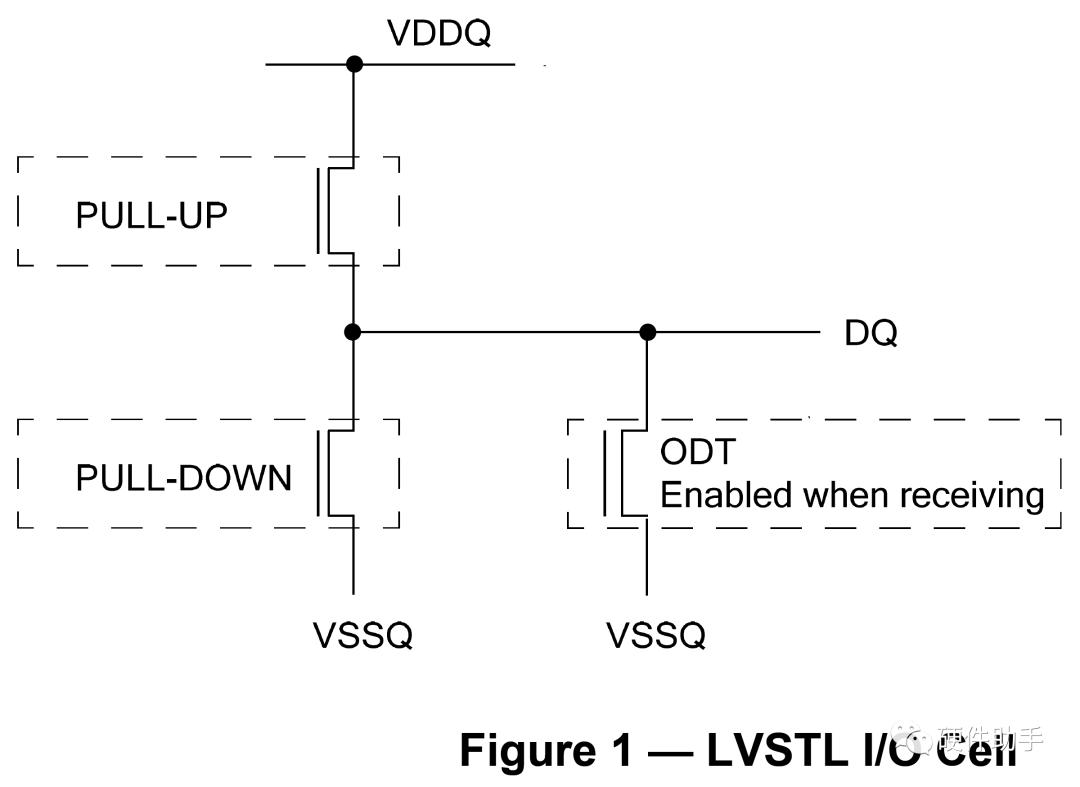

CAз«ҜжҺҘпјҡз»Ҳз«Ҝйҳ»жҠ—зҡ„жЁЎејҸжҺ§еҲ¶пјҡдёҖз§ҚжҳҜдҪҝз”ЁиҠҜзүҮеҶ…йғЁзҡ„з»Ҳз«Ҝз”өйҳ»пјӣеҸҰдёҖз§ҚжҳҜеӨ–йғЁз»Ҳз«Ҝз”өйҳ»гҖӮиҝҷдёӘеҶ…йғЁз”өйҳ»йҡҸзқҖжё©еәҰдјҡжңүз»Ҷеҫ®еҸҳеҢ–пјҢдёәдәҶдҝқиҜҒдҝЎеҸ·жңүеҮҶзЎ®зҡ„з»Ҳз«ҜеҢ№й…ҚпјҢйңҖиҰҒз”ЁеҲ°ZQгҖӮ

ж•°жҚ®дҝЎеҸ·пјӣ

DQSдҝЎеҸ·пјҡеҪ“д»ҺDDRдёӯиҜ»еҸ–дҝЎеҸ·ж—¶пјҢDDRеҸ‘еҮәDQSпјҢеӨ„зҗҶеҷЁж №жҚ®иҝҷдёӘDQSдҝЎеҸ·жқҘеҲӨж–ӯдҪ•ж—¶жҺҘ收数жҚ®пјӣеҫҖDDRдёӯеҶҷж•°жҚ®ж—¶пјҢSoCеҸ‘еҮәDQSпјҢеҶ…еӯҳж №жҚ®DQSжқҘи§ҰеҸ‘ж•°жҚ®зҡ„жҺҘ收гҖӮ

DMIдҝЎеҸ·пјҡеңЁиҜ»еҶҷж“ҚдҪңзҡ„ж—¶еҖҷпјҢLPDDR4ж”ҜжҢҒж•°жҚ®зҝ»иҪ¬(DBIdc)зҡ„еҠҹиғҪгҖӮиҝҷдёӘеҠҹиғҪзҡ„е®һзҺ°жҳҜйҖҡиҝҮиҜ»еҶҷзҡ„ж—¶еҖҷжҺ§еҲ¶MR3еҜ„еӯҳеҷЁзҡ„еҜ№еә”дҪҚжқҘе®һзҺ°зҡ„гҖӮ

ZQеҸӮиҖғз”өйҳ»пјҢ240О© 1%еӨ–жҺҘз”өйҳ»пјҢз”ЁдәҺеҶ…йғЁеҸӮиҖғгҖӮ

д»ҘдёҠе°ұжҳҜй’ҲеҜ№LPDDR4зҡ„з®ҖеҚ•д»Ӣз»ҚпјҢиҜҰз»ҶеҸҜд»ҘеҸӮиҖғsamsungгҖҒSK HynixгҖҒMicronзӯүеҺӮ家зҡ„LPDDR4иҠҜзүҮжүӢеҶҢпјҢжҲ–иҖ…еҸӮиҖғSoCзҡ„DDRжҺ§еҲ¶еҷЁжүӢеҶҢгҖӮ